# ウエハレベルチップサイズパッケージ(WL-CSP) の開発

Development of Wafer-level Chip Size Package (WL-CSP)

浅田敏明\* 天野俊昭\* 日笠和人\* Toshiaki Anano Kazuhito Hikasa

菅原賢一\* 大島宏文\* 小野義視\*2 Kenichi Sugahara Hirofumi Oshima Yoshimi Ono

概要 近年,電子機器の小型化,軽量化及び高機能化が著しく進む中,そこに搭載される半導体パッケージについても小型化,薄肉化,軽量化及び実装基板への高密度実装が要求されてきている。このような状況の中,ウエハレベルチップサイズパッケージ(以下WL-CSPという)と呼ばれる新しい半導体パッケージ技術が注目されている。我々はroll to rollロールによって連続製造したテープ基板とウエハを貼り合わせることにより,コスト低減と納期の短縮化を図り,外部接続電極を樹脂突起構造とすることにより高信頼性を確保したWL-CSPを開発した。本報では、当社オリジナルのWL-CSPに関する構造,製造プロセス,特徴,試作結果及び信頼性評価結果について報告する。

# 1. はじめに

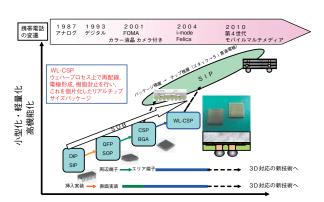

近年、携帯電話、モバイルコンピュータ、パーソナル携帯情報機器 (PDA)、デジタルスチルカメラ (DSC) などに代表されるエレクトニクス製品は、小型化、軽量化及び高機能化が飛躍的に進んでいる。これらの市場動向に伴い、エレクトロニクス製品に搭載される半導体パッケージについても、小型化、薄肉化、軽量化及び実装基板への高密度実装が強く要求されてきている(図1)。

このような背景のもと、ウエハ状態のままでパッケージングまで行うWL-CSPと呼ばれる新しい半導体パッケージ技術が注目されている。WL-CSPは、ウエハプロセスで再配線や電極形成→樹脂封止→ダイシングまでを全て行い、最終的にウエハを切断した半導体チップの大きさがそのままパッケージの大きさであるため、小型化及び軽量化の観点からも理想的であるといえ、既に携帯電話などに採用されている。我々は、はんだ付きテープ基板とウエハを貼り合わせる新規の工法によって、短納期への対応と低コスト化を実現しうるWL-CSP製造技術の開発を行った。更に、実装基板との接続電極を樹脂突起電極構造としたことにより、高い接続信頼性が確認できた。今回、新製造法により開発された高接続信頼性WL-CSPについて報告する。

## 2. 当社製WL-CSP開発の背景

当社では、軽量化、薄型化及び高速化に対応する半導体パッケージ用インターポーザとしてFBTI® (Flexible Bumped

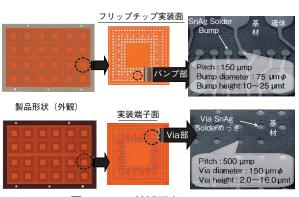

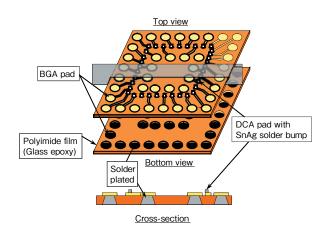

Tape Interposer) 1) を開発し2001年より上市している。これは 従来のワイヤボンディング接続と比較して、省スペース化と高 周波に適しているフリップチップ接続を前提としたインターポーザである。これは図2及び図3に示すとおり、半導体チッ

図 1 半導体パッケージの技術動向 Trend of semi conductor package technology.

図2 FBTI外観写真 Appearance of FBTI.

<sup>\*</sup> 研究開発本部 環境・エネルギー研究所

<sup>\*2</sup> 設備部 第一生産技術開発センター

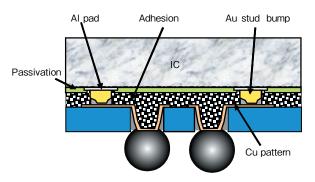

図3 FBTI構造図 Schematic structure of FBTI.

プと電気的接続を行うためのSnAgはんだバンプがテープ基板上に形成されている。このはんだバンプ付きテープ基板であるFBTIは、低コストを狙ったroll to rollと呼ばれる連続的方法で製造している。

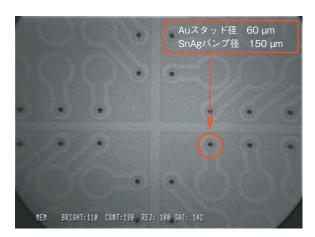

FBTIのアプリケーションとしては、(㈱東芝セミコンダクター社においてTQON (Thin Quad Outline Non-Leaded) 及びSBM (System Block Module) と呼ばれる半導体パッケージの実績がある。これらの製品では、半導体チップ上に形成したAuスタッドバンプとFBTI上のSnAgはんだバンプをフリップチップ接続する構造を採っており、アプリケーションとしても高い信頼性が確認されている。これらの実績から、FBTIの低コスト化を狙ったテープ基板の製造技術と、それを使用するアプリケーションにおいて、信頼性が確認されているフリップチップ接続による接続技術を組み合わせることにより、当社オリジナルのWL-CSPを具現化する可能性があると判断し開発に着手した。

## 3. 当社製WL-CSP開発のコンセプト

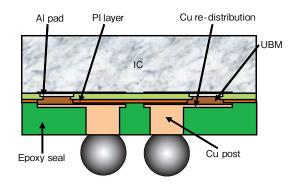

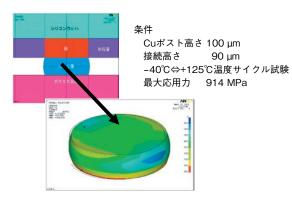

既に市場において採用実績のある銅ポストタイプのWL-CSPと当社製WL-CSPの構造をそれぞれ図4と図5に示す。市場における他社製WL-CSPは70~100μmの銅ポストをウエハ再配線上に形成することで、実装基板との接続信頼性を確保することが構造上の特徴である。銅ポストタイプWL-CSPの製造は、ウエハ上で引き回し用の回路を形成する再配線形成→銅ポストの形成→樹脂封止を行うことから、ウエハプロセスに必要な特殊な製造装置を保有する必要がある。また、構造上の特徴である銅ポストを形成する長時間のめっき工程が必要であり、更に、ウエハを受け取ってから製造を開始するため完成までの製造時間が長く掛かるといわれている。

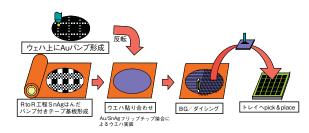

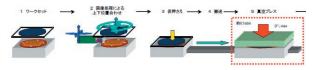

一方、当社製WL-CSPの製造プロセスは、樹脂突起電極付きテープ基板の製造、ウエハへのAuスタッドバンプの形成及びウエハとテープ基板の貼り合せの三つに大きく分けられる(図6)。樹脂突起電極付きテープ基板の製造プロセスとしては、既にFBTIで製造実績のある roll to rollによるテープ基板の製造法を適用することで低コスト化が可能である。また、設計情報が事前に入手できればテープ基板の製造ができることから、ウエハ入手後にはAuバンプの形成及びテープ基板とウエハの

図4 市販のWL-CSPの構造図 Schematic structure of commercially available WL-CSP.

図5 当社製 WL-CSPの構造図 Schematic structure of Furukawa's WL-CSP.

図6 当社製 WL-CSP 製造プロセスのコンセプト Concept of Furukawa's original WL-CSP manufacturing process.

貼り合せ以降の工程となるため短納期への対応が可能であると 考える。

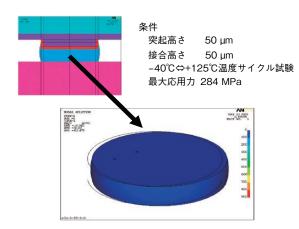

当社製WL-CSPの構造的な特徴は、樹脂突起電極と呼んでいる外部接続用電極が樹脂を内包していることが挙げられる。一般的に、WL-CSPは外部接続用電極部分にはんだボールを供給して、実装基板に実装されて使用される。基板に実装された半導体パッケージなどの電子部品の実装信頼性は温度サイクル試験と呼ばれる試験により評価されることが多く、はんだボールを介して基板に実装するWL-CSPの場合、シリコンである半導体チップとFR-4と呼ばれる実装基板の熱膨張係数の差によって、はんだボールに応力が掛かり、WL-CSPとはんだボールの間又は実装基板とはんだボールの間でクラックが生じる。このクラックが成長する疲労破壊により断線が発生することが一般的な不良要因である。つまり、信頼性試験の試験条件において、はんだボールに掛かる応力が小さいほど、破壊に至るまでの寿

命が長くなるといえる。図7及び図8に示すとおり外部接続電極構造のシミュレーションによる応力解析では、いわゆる銅ポスト構造と比較して樹脂突起構造の方が、はんだ接合部における最大応力を軽減することができ、接合寿命の改善が期待できる。

また、当社製WL-CSPは、ウエハ(半導体チップ)上のAuスタッドバンプとテープ基板上のはんだバンプがフリップチップ接合している構造をとっている。このAuとSnAgによるフリップチップ接合は、前述したとおり半導体パッケージとして既に実績がある工法である。高周波対応としても有利な構造であるので、今後市場に出てくるDDR3-DRAMと呼ばれる高速メモリーにも対応できると考える。

図7 他社製 WL-CSP の応力解析 Calculated stress distribution of a commercially available WL-CSP.

図8 当社製 WL-CSP の応力解析 Calculated stress distribution of Furukawa's WL-CSP.

## 4. 当社製WL-CSPの技術的課題

他社製WL-CSPの製造工程では、ウエハ上で引き回し用の回路形成を直接行うことから、ウエハに直接感光性樹脂の塗布・露光・現像、金属めっき・エッチングなどの工程がある。露光用のマスクを精度よく合わせるなどの技術的ポイントはあるもののウエハプロセスの採用で対応しているのが一般的である。一方、当社製WL-CSPは前述したとおり他社製と全く異なる工法で、ウエハ上に形成するAuスタッドバンプとテープ基板上に形成するはんだバンプをフリップチップによって接合する工程を前提としていることから、二つの大きな課題があった。1つは、テープ基板に高い寸法精度が求められること、もう1つ

は、テープ基板とウエハを精度よく貼り合わせることである。

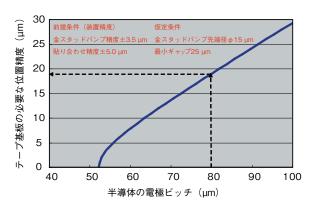

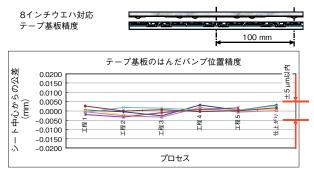

テープ基板の寸法精度については半導体チップの電極ピッチ などの設計によって求められる精度に違いはあるが、例えば Auスタッドバンプの形成精度 ± 3.5 μm, テープ基板とウエハの 搭載精度±5 μmの機械精度と、Auスタッドバンプ先端径φ15 μm,最小ギャップ25 μmを前提とすると図9の関係が導きださ れる。つまり、8インチウエハで半導体の電極ピッチを80 μm と想定した場合、テープ基板のはんだバンプの位置精度は 100 mm (8インチウエハのセンターから周辺までの距離) に対 して約19 μm以内に抑える必要がある。将来, 半導体チップ の電極ピッチが更に狭くなる場合や、ウエハサイズが大型化し て12インチウエハに対応する場合は、①Auスタッドバンプの 先端径を小径化する,②最小ギャップを狭く設定する,③テー プ基板の精度をより上げるなどの方策が必要となる。当社製 WL-CSP用においてはテープ基板の製造に, roll to rollの連続 製造方法を採用していることや、変形しやすいテープ基材を採 用していることから、基材の取り扱い方法や変形を抑える工夫 が重要なポイントとなっていた。その中でも、基材を固定する キャリヤの選定と固定方法の工夫や回路形成方法などの方策を 組み合わせることによって、位置精度を±5 μm以内にするこ とを可能とした(図10)。更に寸法精度を向上させるには、テー プを製造する環境(温度,湿度)を管理する必要がある。

もう1つの課題であるテープ基板とウエハを位置合わせして 貼り合わせる工程も当社製WL-CSP固有の工程である。当然, この装置の搭載精度によって、テープに求められる精度に影響 を及ぼすことから、できるだけ搭載精度のよい装置が必要で あった。この搭載精度 $\pm 5~\mu m$ を仕様とした装置について市場

図**9** テープ基板に求められる位置精度 Accuracy requirement for tape substrate.

**図10** テープ基板の位置精度 Accuracy of tape substrate.

図11 アライメントプレス装置 Appearance of alignment press machine.

図12 軟 X 線による位置合わせ精度の確認 Soft X-ray image of WL-CSP.

の調査を行ったが、独特な工程のためこの仕様に合致する装置 が見つからなかった。そこで、社内の生産技術開発センターが アライメントプレス装置の開発及び製造を行い、現在はその装 置を用いてサンプル作成及び評価を実施している(図11)。現 状では、テープ状基板とウエハを張り合わせた場合の、Auス タッドバンプとはんだバンプの位置合わせ精度についても十分 良好であることを確認している(図12)。

## 5. 信頼性評価

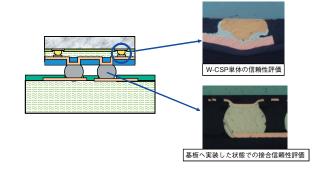

信頼性評価は次の2つに分けられる。1つはWL-CSP(パッ ケージ) 単体の信頼性評価(以下、一次実装信頼性評価という) で、もう1つはWL-CSPをはんだボールで基板に実装した場合 の信頼性(以下, 二次実装信頼性評価という)である。

サンプルチップには図13に示すとおり、大きさ6.30 mm角 で、電極がチップ周辺部に48ピンある評価用TEGチップを使 用した。

#### 5.1. 一次実装の信頼性

テープ基板は、TEGチップとテープ基板からなるWL-CSP を二次実装信頼性評価用の基板に実装した場合に、デイジー チェーンになるように設計を行った。テープ基板とウエハの貼 り合わせ条件については、Auスタッドバンプの変形状態、 SnAgはんだのAuスタッドバンプへの付き回り状態、絶縁層

図13 サンプル形状 Sample for reliability evaluation.

の厚さなどから最適化を行った。

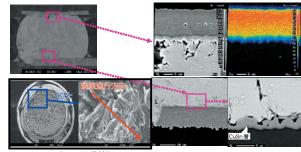

評価内容については、表1にある項目について、外部接続電 極部を四端子法で導通の有無を確認し、外観及び断面の観察に より異常の有無の確認を行った。特に断面観察においては、 Au/SnAg接合部分のクラック発生状態や半導体チップ/接着 剤層及びテープ基板/接着剤層の剥がれについて注視した。

その結果、今回作成評価したサンプルの信頼性試験において は、表1に示す通り全サンプルが合格という良好な結果が得ら れたことから、半導体パッケージとして信頼あるものといえ、 改めてAu/SnAgのフリップチップ接合の信頼性が確認され

一次実装頼性結果 表 1 Conditions and results of PKG reliability test.

| Test                     | Condition                              | Failure rate |

|--------------------------|----------------------------------------|--------------|

| Thermal shock            | -65 ⇔ 150°C 1,000 cycles               | 0/22         |

| High temp. storage       | 150℃ 1,000 hrs                         | 0/10         |

| Autoclave                | 121℃ 85%RH 500 hrs                     | 0/10         |

| Pre-conditioning (JEDEC) | 85℃ 85%RH 168 Hrs<br>250℃ reflow 3pass | 0/22         |

#### 5.2. 二次実装の信頼性

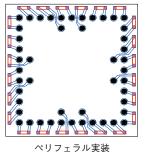

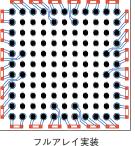

実装用評価基板は、実装基板として最も一般的であるFR-4 を使用した。実装端子ピッチは0.5 mmとし、はんだボールに は直径0.3 mmのSnAgCuはんだを使用した。サンプルの評価 は、チップの厚みと実装するはんだボールの配置に注目をした 評価を行ったのでその評価結果を次に示す。1つは、チップ厚 が530 umで実装のはんだボールを周辺部の48箇所(基板に実 装した場合にデイジーチェーンを形成するのに必要な最少数) としたペリフェラル実装とした場合と、もう1つは、チップ厚 が200 μmではんだボールを0.5 mmピッチでフルアレイに実

図14 実装状態の比較 Comparison of surface mounting methods.

装した場合である(図14)。

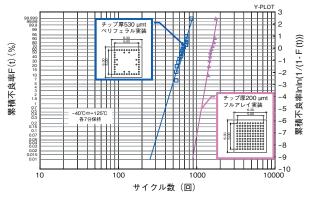

熱衝撃試験(-40℃⇔125℃ 各7分保持)において、実装基 板とWL-CSPで形成されたデイジーチェーンの導通をモニタ リングしながら信頼性評価を行った結果を図15のワイブル図 で示す。青い線は、半導体チップ厚が530 µmで、はんだボー ルによる実装がペリフェラル実装の試験結果である。これは, 当初の開発目的であった1%不良確率において、400サイクル 以上をクリアできたことを示している。また、チップ厚 200 μmのパッケージ(はんだボールを除いたパッケージ総厚 280 μm) で、はんだボールによる実装がフルアレイ実装の試験 結果が赤い線である。こちらにおいては更に良好な結果が得ら れており、小面積だけではなく薄型パッケージの可能性が見え てきた。他社製WL-CSPにおいては、銅ポストの高さが約 100 μmであることや、その銅ポストを埋め込むために樹脂で 厚く封止していることから、発生する大きな応力のためにチッ プを薄くすることが難しいと言われている。これに対して当社 製WL-CSPはウエハとテープ基板を貼り合わせた後にバック グラインドを行うことから、今回評価を行ったパッケージより もチップ厚を薄くできる可能性がある。

また, 熱衝撃試験後の断面観察による故障解析から, 破壊の 発生ははんだボールと実装基板若しくはWL-CSPの間で起 こっており、更に詳しく観察すると銅がはんだに拡散してでき た硬いCuSn化合物層と柔らかいはんだの界面に亀裂が生じて いる。破壊の発生箇所については、半導体チップと基板の熱膨 張係数の差によって大きな応力が掛かる、四隅のはんだボール への影響が大きく、実際の評価においても導通不良は四隅のは んだボールから多く発生することが確認されている。

はんだボールを剥離した面の観察を行うと、WL-CSPのコー ナーから中心方向に対して垂直な向きに連続的な縞模様が見ら れる(図16)。これらの故障解析より、半導体と実装基板の線 膨張率差によって発生する繰り返しひずみにより、硬い金属化 合物層と柔らかいはんだ層の間で亀裂が起こり、この亀裂が成 長する疲労破壊であることが判る。樹脂突起電極という独特な 構造を持つ当社オリジナルのWL-CSPにおいても、はんだボー ルで基板に実装する一般のBGA部品と同様な破壊モードであ ることから、実装基板に対する信頼性の考え方はBGA部品と 同じであるといえる。現在も更なる薄型化及び高信頼性を確保 すべく改良法の検討を継続している。

図15 二次実装信頼性結果 Test results of solder joint reliability.

はんだボールを剥離した面

図16 故障解析 Analysis of failure.

# 6. おわりに

今回、小型化及び軽量化の観点で理想的といわれる WL-CSP について、従来のウエハプロセスと全く異なるテープ基板とウ エハを貼り合わせる工法の開発を行った。新しい工法により短 納期への対応と低コスト化を両立でき、更に外部接続電極構造 に樹脂を内包する構造の採用により実装基板への接続信頼性を 確保できることを確認した。チップの厚さが200 μmの薄型 パッケージ(はんだボールを除いたパッケージ総厚280 μm) に ついても良好な信頼性が得られたことから、WL-CSPによる薄 型パッケージの実現性を確認できた。

他社製WL-CSPはウエハプロセスを使って製造を行うこと から、歩留まりの良いウエハに適用されているが、当社製 WL-CSPにおいては良品のチップのみを使ったフリップチップ ボンダーによる個別実装も可能である。また、電極数の多い半 導体においては、チップの下面に実装端子を全て配置(fan-in) できない場合もあるが、チップの個別実装においては、チップ の外側にも実装端子を配置(fan-out)も可能であることから、 樹脂内包外部接続用電極を有する高信頼性半導体パッケージと しての展開が期待できる。

#### 参考文献

1) 日笠和人, 天野俊昭, 掛上俊哉, 菅原賢一, 豊田尚之: "FBTI® (Flexible Bumped Tape Interposer)の開発,"古河電工時報, **112** (2003), 55.