# 超高Δ石英ガラス系平面光導波路の開発

## Development of Ultra-High \( \Delta \) Silica-Based Planar Lightwave Circuit

高橋正典\* Masanori Takahashi 内田泰芳\* Yasuvoshi Uchida

山﨑慎太郎 Shintaro Yamasaki

長谷川淳一\* Junichi Hasegawa

#### 〈概要〉

光通信ネットワークにおいて,石英系平面光導波路 (planar lightwave circuit: PLC) 技術を利用し た光部品が多数実用化されている。高速,大容量伝送化を実現するために,次世代の光通信ネットワー クに使用されるPLCデバイスには小型化,低コスト化,高密度集積化が求められている。これらの 特性を実現するためにはPLCを構成するコアとクラッドの比屈折率差Δを高める必要がある。従来 使用されてきた、コアに添加するドーパントをGeO2から、より屈折率の高いZrO2に変更する事で 5%以上の $\Delta$ を有する超高 $\Delta$  PLC を実現した。本報告では $ZrO_2$ -Si $O_2$ 超高 $\Delta$  PLC の低損失化,超高 $\Delta$ PLCによる超小型のコヒーレントミキサ、超高 $\Delta$  PLC とシングルモードファイバ (SMF) との低損失 接続技術の開発に関して報告する。

#### 1. はじめに

光通信システムにおいて、石英系平面光回路(planar lightwave circuit: PLC) を使用したデバイスが多数実用化され、 広く商用展開されている。特にデジタルコヒーレント受信方式 を利用したDual-polarization quadrature phase-shift keying (DP-QPSK) 信号方式の100 Gbit/sの高速通信システムに導入 され、今後本格的に需要が増加すると考えられる、PLCを用 いたコヒーレントミキサに関する研究開発が行われている1)。 コヒーレントミキサを含めた、次世代のPLCデバイスには小 型化,低コスト化と同時に高密度集積化が求められる。さらに, 実際の製品に適用するためには上記の特性を満たすと同時に, 低伝搬損失, ファイバとの低接続損失が必要であり, 低偏波依 存性, 製造性, 信頼性に関しても考慮する必要がある。近年, 次世代導波路デバイスの研究開発が多数報告されており、代表 的なものとして,石英系導波路<sup>2),3)</sup>,InP系導波路<sup>4)</sup>,Si細線 導波路<sup>5)</sup>が検討されている。これらの材料はそれぞれ一長一短 がある。InP導波路、Si細線導波路はコアとクラッドの比屈折 率差 △ が大きい材料であるため、高密度集積化、チップサイズ の小型化には有利である。しかしながら、伝搬損失、ファイバ との接続損失が大きい点が問題となる。一方、石英系導波路は △が小さい材料であるため、高密度集積化、小型化が課題とな るが, 低伝搬損失, ファイバとの接続性に加え, 低偏波依存性, 優れた製造性を有している。このため、Δが大きくできる材料 が開発できれば、チップサイズの小型化が実現する。

本報告では次世代の導波路デバイスを実現するために最適な 特性を有する石英系PLCの開発に関して報告する。第2節では PLCを小型化するための超高△化の設計を示す。第3節では設 計した超高ΔPLCの作製工程について,第4節では超高ΔPLC の基本特性についてそれぞれ示す。第5節では超高ΔPLCによ り実現した小型のコヒーレントミキサの試作結果を示す。第6 節では超高 Δ PLC に最適化した構造を有するスポットサイズ コンバータ (spot size converter: SSC) を設計, 試作した結果 について報告する。

#### 2. 超高Δ PLCの設計

通常のPLCはSi基板上に堆積したクラッド内部に埋め込ん だコアを光が伝搬する構造となっている。PLCのチップサイ ズは主に導波路の最小曲げ半径により決まる。最小曲げ半径を 小さくするためには△を高め、コアに光を強く閉じ込める必要 がある。

### 2.1 GeO<sub>2</sub>-SiO<sub>2</sub> PLCの超高△化限界

高 $\Delta$ 化のためには $GeO_2$ の添加量を増やす必要があるが、 GeO<sub>2</sub>の添加量を増やすとガラスの軟化点温度が下がり、熱膨 張係数 α が大きくなり、PLCの製造工程において火炎堆積法 (flame hydrolysis deposition: FHD) 等の高温プロセスで製造 性に問題が生じ、実用化を考慮したGeO<sub>2</sub>-SiO<sub>2</sub> PLCでは2.5% OO(1000) の  $\Delta$  が上限となる  $^{6)}$  。

#### 2.2 超高 Δ化の目標設定

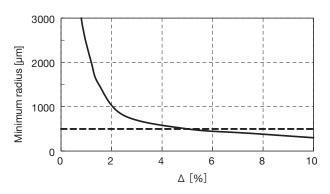

次世代PLCに期待される小型化、高密度集積化を実現する ための、△について検討した。まず△と導波路に許容される最 小曲げ半径の関係をシミュレーションにより明らかにした。本 シミュレーションではBPM法 (beam propagation method) に より、各Δにおいて異なる曲げ半径を有する導波路を伝搬した 際の伝搬損失を計算した。損失が0.01 dB増加する曲げ半径を 最小曲げ半径とした、計算結果を図1に示す。現行のPLCの多 くは1.5%以下のΔに設計されており、最小曲げ半径はおよそ 1500  $\mu$ m  $\sim$  2000  $\mu$ m である。 $GeO_2$ -Si $O_2$  PLC の上限となる 2.5%

<sup>\*</sup> 研究開発本部 情報通信・エネルギー研究所

のΔの場合、最小曲げ半径はおよそ800 μmとなる。次世代の PLCデバイスに最適となる特性を実現するため、競合技術で あるInP等の半導体導波路<sup>7)</sup>と同程度となる500 μm以下の最 小曲げ半径を目標とした場合Δを5%以上に設定する必要があ る。

図 1 最小曲げ半径と△の関係 Relationships between  $\Delta$  and minimum bending radius.

### 2.3 超高 Δ PLC を実現するためのドーパント選定

超高 △ PLC を実現するためのドーパント材料として GeO。よ りも屈折率が高く、熱膨張係数 α の小さい材料を選定の対象と した。各材料の特性を表1に示す $8^{1,9}$ 。候補となる材料はドー パントしてSiO<sub>2</sub>ガラスに添加して使用するため、SiO<sub>2</sub>と固溶 体を形成する、化学的親和性が高い材料が望ましい。これらの 材料の中で、SiO<sub>2</sub>との親和性が高い材料はZrO<sub>2</sub>とHfO<sub>2</sub>(であ り、ZrO<sub>2</sub>とHfO<sub>2</sub>を比較すると、ZrO<sub>2</sub>の方がより屈折率が高 いこと、Zr原料の価格が安く埋蔵量が豊富で入手性が良好で ある事<sup>10)</sup>からZrO<sub>2</sub>をドーパントとして選定した。

超高 Δ PLCのドーパント検討 夷1 Characteristics of dopants for ultra-high  $\Delta$  PLC.

| Refractive index | a × 10-6                                     | Affinity to SiO <sub>2</sub>                                     |

|------------------|----------------------------------------------|------------------------------------------------------------------|

| 2.45             | 9.0                                          | Poor                                                             |

| 2.20             | 5.0                                          | Poor                                                             |

| 2.31             | 2.0                                          | Poor                                                             |

| 2.17             | 8.0                                          | Good                                                             |

| 2.02             | 6.5                                          | Good                                                             |

| 1.70             | 12.0                                         | Good                                                             |

| 1.45             | _                                            | _                                                                |

|                  | 2.45<br>2.20<br>2.31<br>2.17<br>2.02<br>1.70 | 2.45 9.0   2.20 5.0   2.31 2.0   2.17 8.0   2.02 6.5   1.70 12.0 |

#### 3. ZrO<sub>2</sub>-SiO<sub>2</sub> PLCの作製工程の最適化

ZrO<sub>2</sub>をドーパントとしたZrO<sub>2</sub>-SiO<sub>2</sub> PLCを作製するため, まずSi基板上にSiO<sub>2</sub>からなるアンダークラッドを堆積させ、 アンダークラッド上にZrO<sub>2</sub>-SiO<sub>2</sub>ガラスをスパッタ法により成 膜した。成膜後、1000℃以上の温度でアニール処理を行い、成 膜時に生じる欠陥を除去した。次にフォトリソグラフィーとド ライエッチングによりコアをパターンニングし、最後にオー バークラッドで埋め込みを行った。次項では、 $ZrO_2$ -Si $O_2$  PLC の伝搬損失を低減するために行った工程の最適化について示

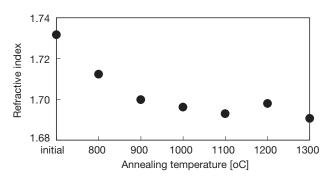

#### 3.1 ZrO<sub>2</sub>-SiO<sub>2</sub>ガラスのアニール処理

コア成膜直後にはガラスに酸素欠陥が存在し、欠陥による光 の吸収で伝搬損失が大きくなるため、酸素雰囲気中でアニール 処理を行い、酸素欠陥の除去を行った。ガラスの屈折率は光と ガラスを構成する電子との相互作用によって決まる。ガラスを イオンの集合体と考えれば、屈折率nは各イオンの分極率a. Nを単位体積内の分子数とすると、ローレンツ-ローレンツの 式から次式で表される。

$$\frac{-n^2 - 1}{n^2 + 2} = \frac{4\pi}{3} \sum_{j} N_j \tag{1}$$

(1) 式から、分極率の高いイオンが存在すれば屈折率が高く なる。そのため、酸素欠陥が存在するガラスは屈折率は高くな

$2 CZrO_2-SiO_2$ ガラスの屈折率とアニール温度との関係を 示す。この結果から1000℃以上の温度でアニールする事で酸 素欠陥が除去できる事を示している。

図2 ZrO2添加SiO2ガラスの屈折率とアニール温度の関係 Relationships between refractive index of ZrO<sub>2</sub>-SiO<sub>2</sub> glass and annealing temperature.

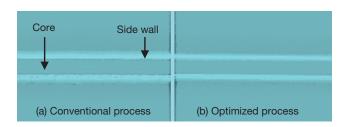

### 3.2 ZrO<sub>2</sub>添加ガラスのドライエッチング

PLCの伝搬損失の原因の一つに、コアのパターンをドライ エッチングにより形成する際に生じるコアの側壁荒れによる光 の散乱が挙げられる。図3にパターンニング後のコアの形状を 示す。PLCの製造プロセスではコアとなるガラス膜を成膜後、 フォトリソグラフィーとドライエッチングを用いてコアをパ ターンニングする。ZrOoは通常のPLCのコアのドーパントと して使用されているGeO2と比較して、ハロゲン系ガスを反応 ガスとして用いるプラズマエッチングでは反応生成物の蒸気圧 が低い<sup>11)</sup>。ZrO<sub>2</sub>は難エッチング材料でZr-O結合が強い<sup>11)</sup>ため, 通常のPLCと同じプロセス条件で加工を行うと図3(a)に示す ように大きな側壁荒れが生じる。そこでZrO2添加SiO2ガラス の加工プロセスの最適化を行い、コアの側壁荒れを大幅に低減 する事に成功した。加工プロセス最適化後のコアを図3(b)に 示す。

ドライエッチング後のZrO2添加SiO2ガラスの写真 図3 Picture of the ZrO<sub>2</sub> - SiO<sub>2</sub> glass formed by dry etching.

### 4. ZrO<sub>2</sub>-SiO<sub>2</sub> PLCの基本特性

第3節で示した工程によりZrO2-SiO2 PLC試作した。成膜し たZrO₂-SiO₂ガラスは1000℃以上の温度でアニール処理を行 い、最適化したプロセス条件でコアのパターンを形成した。試 作したZrO<sub>2</sub>-SiO<sub>2</sub> PLCのΔは5.5%とし、コアサイズは3× 3 μmとした。本節で示す光学特性は全て波長1550 nmで測定 を行った。

### 4.1 ZrO<sub>2</sub>-SiO<sub>2</sub> PLCの伝搬損失

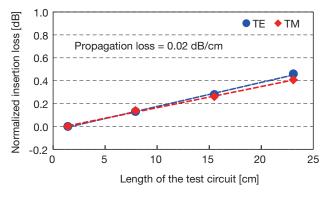

図4に示す渦巻き状の回路を使用し、TE(transverseelectric)とTM (transverse-magnetic) 偏光で、長さの異なる 複数の回路の挿入損失を測定し、回路長に対する損失の増分を 伝搬損失として算出した。図5に最も回路長が短い回路の挿入 損失で正規化した挿入損失と回路長の関係を示す。伝搬損失は TE, TM 偏光に対してそれぞれ 0.021 dB/cm と 0.018 dB/cm で あった。この伝搬損失はInP導波路 $^4$ と比較して1/100であり、 通常の $GeO_2$ -Si $O_2$  PLC<sup>12)</sup> と同程度の低損失が実現した。

図4 伝搬損失測定に使用した回路図 Circuit layout for propagation loss measurement.

図5 ZrO2-SiO2 PLCの正規化挿入損失と回路長の関係 Relationships between normalized insertion loss of the ZrO<sub>2</sub>-SiO<sub>2</sub> PLC and circuit length.

#### 4.2 最小曲げ半径

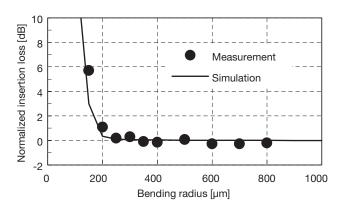

測定には異なる曲げ半径を有する曲げ導波路と直線導波路を 組み合わせた波状回路を使用した。波状回路の挿入損失と曲げ 導波路の曲げ半径の測定値とシミュレーション値の結果を図6 に示す。回路の挿入損失が増加しはじめる点を最小曲げ半径と すると、試作したZrO<sub>2</sub>-SiO<sub>2</sub> PLCでは、最小曲げ半径を 300 μmに設計可能なことが分かった。これは通常のPLCと比 較して1/5以下の曲げ半径が実現可能な事を示しており、大幅 な小型化、高密度集積化が期待できる。

異なる曲げ半径を有する回路の正規化挿入損失と曲げ半 径の関係 Relationships between normalized insertion loss of the circuit and bending radius.

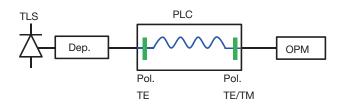

### 4.3 偏波消光比測定

試作したZrO<sub>2</sub>-SiO<sub>2</sub> PLC の偏波消光比 (polarization extinction ratio: PER) の測定系を図7に示す。波長可変光源 (tunable laser source: TLS) を光源として使用した。デポラライザ (depolarizer: Dep.) を通した後、PLC両端に偏光子 (polarizer: Pol.) をセットしたサンプルにTLS光を入射した。PLCからの 出力を光パワーメータ (optical power meter: OPM) で測定し た。PLCの入射端にはTE偏光のPol.をセットし、出射端には TE, TM偏光のPol.をそれぞれセットした。PLCの回路には 曲げ損失測定に使用した物と同様の波状回路を使用した。測定 の結果、PERは29 dBであった。

偏波消光比測定に使用した測定系 Setup for PER measurement.

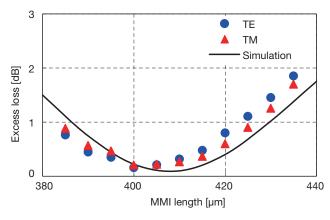

### 4.4 MMIカプラ特性

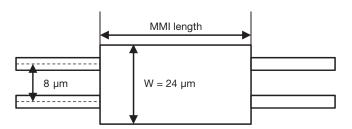

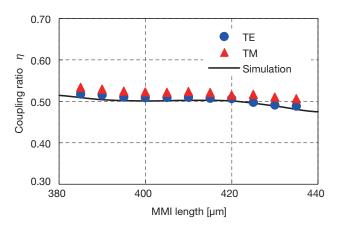

ZrO<sub>2</sub>-SiO<sub>2</sub> PLCが機能回路に適用可能かを検証するために MMI (Multi-Mode Interference) カプラを設計, 試作した。使 用したMMIカプラの模式図を図8に示す。MMI幅Wを

24 μm, 入出力部の導波路ピッチを8 μmとした。MMI長と結 合効率 η の関係を図9に、MMI 長と過剰損失の関係を図10 に それぞれ示す。図9と図10にそれぞれプロットで示す測定値に 対し、実線で示すシミュレーションの値はいずれもよく一致し ている。結合効率が0.5となる点において、過剰損失は0.2 dB であった。この結果から、ZrO<sub>2</sub>-SiO<sub>2</sub> PLCはMMIカプラを使 用した機能回路に適用できる事を確認した。

試作したMMIカプラの模式図 図8 Schematic diagram of fabricated MMI coupler.

図9 試作したMMIカプラの結合効率 Coupling ratio of fabricated MMI coupler.

図10 試作したMMIカプラの過剰損失 Excess loss of fabricated MMI coupler.

### 5. ZrO<sub>2</sub>-SiO<sub>2</sub> PLC による超小型コヒーレントミキサ

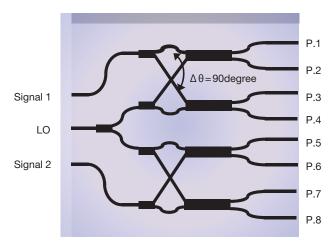

ZrO<sub>2</sub>-SiO<sub>2</sub> PLCを使用し、90°ハイブリッドミキサを設計、 試作した。図11に設計したミキサの構成図を示す。TE, TM

各偏光状態の信号光がSignalポートに入射され, LO(Local oscillator) ポートに入射された局部発振光と上下のミキサでそ れぞれ合波される。ミキサを構成する光カプラは1×2 MMI, 2×2 MMIカプラで構成され、分岐比、結合効率はそれぞれ 50%に設定されている。上下のミキサ部には90°の位相差( $\Delta \theta$ ) を与える遅延線を配置しており、信号光とLO光の干渉によっ て光学的に復調された光が各出力ポートから出力される。本設 計では第4節で示したZrO<sub>2</sub>-SiO<sub>2</sub> PLCと同様にΔは5.5%, コア の膜厚は3 µmに設定し、回路の最小曲げ半径は400 µmに設 定した。

図11 設計したコヒーレントミキサの構成 Schematic diagram of designed coherent mixer.

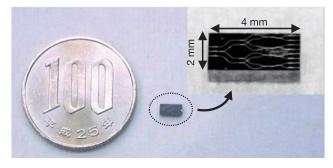

図12に試作したコヒーレントミキサの写真を示す。ミキサ のチップサイズは4 mm×2 mmであった。この値は従来の チップサイズである $12~ ext{mm} imes 12~ ext{mm}^1)$ と比較して大幅な小型 化に成功している。従来品は偏波ビームスプリッタ (polarization beam splitter: PBS) が集積されいる点で今回試 作したミキサとは構成が異なるが、PBSのサイズを考慮しても ZrO<sub>2</sub>-SiO<sub>2</sub> PLCによる顕著な小型化の効果が確認できた。また、 このチップサイズは競合技術であるInP系導波路によるコヒー レントミキサ4)と同程度のサイズである。

図12 試作したコヒーレントミキサの写真 Picture of fabricated coherent mixer.

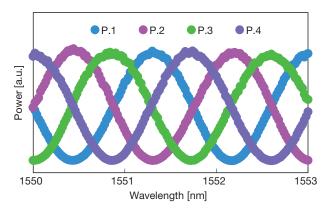

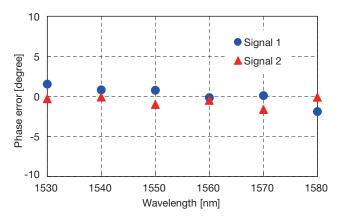

コヒーレントミキサから出力される干渉波形の位相特性を評 価するために、コヒーレントミキサにスプリッタと遅延線から なる追加回路を接続した。これによりコヒーレントミキサは

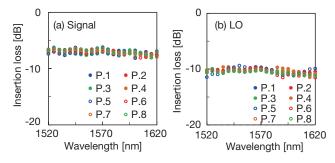

マッハツェンダ干渉計 (Mach-Zehnder interferometer: MZI) となる。MZIの自由スペクトル領域 (free spectral range: FSR) は200 GHzに設定し、波長可変光源を用いて干渉波形を 観測した。ミキサチップの上部アームの出力ポートであるP.1 ~P.4からの出力波形を図13に示す。この結果, 試作したコヒー レントミキサからの出力波形は90°の位相差が実現している事 を確認した。下部アームについても同様の測定を行った。 図14に出力波形から算出した位相誤差を示す。図14から、位 相誤差は波長1530 nmから1580 nmの範囲で±3°以下であっ た。図15に試作したミキサの挿入損失を示す。この挿入損失 にはミキサチップと入出力部のSMFとの結合損失は含まれて いない。入射光はTE偏光とした。シグナルポートの挿入損失 は約6.5 dBであり、C+Lバンド帯で大きな波長依存性がない 事を確認した。挿入損失には90°ハイブリッドミキサでシグナ ル光が分岐される際の原理損失6.0 dBに加え、MMIカプラの 過剰損失0.2 dBが2ヶ所分が含まれており、それ以外の大きな 過剰損失が発生していない事を確認した。

図13 コヒーレントミキサから出力された干渉波形 Interference patterns of coherent mixer.

図14 コヒーレントミキサの位相誤差 Phase error of coherent mixer.

**図15** (a) シグナルポートと (b) LO ポートの挿入損失 Insertion loss of (a) signal port and (b) LO port.

### 6. ZrO<sub>2</sub>-SiO<sub>2</sub> PLCの低損失接続技術

ZrO<sub>2</sub>-SiO<sub>2</sub> PLCはΔが高く、コアのサイズが小さい事から SMFとの接続損失が大きくなる。今回試作したZrO<sub>2</sub>-SiO<sub>2</sub> PLC ではSMFとの接続点に導波路幅を広げた簡易的なSSC (Spot-Size Converter) を使用しており、2.7 dB/facetの接続損失で あった。従来のPLCと同程度となる0.5 dB/facet程度の接続損 失を実現するためには、ZrO2-SiO2 PLCから入出力される光の スポットサイズを厚さ方向にも広げる必要がある。そこで, ZrO<sub>2</sub>-SiO<sub>2</sub> PLCとSMFの接続に適したSSCの構造を検討した。

### 6.1 SSC の構造検討

スポットサイズを縦横両方向に拡大する方法として、テーパ SSC<sup>13)</sup>は最も効果的にスポットサイズを拡大できるSSCのひと つであるが、テーパSSCをZrO<sub>2</sub>-SiO<sub>2</sub> PLCに適用するには下記 の問題がある。

- ・SMFのコア径は10 um程度であるため、テーパSSCでス ポットサイズを拡大する場合, これ以上にコアの膜厚を厚 くする必要がある。

- · ZrO<sub>2</sub>-SiO<sub>2</sub> PLCのコアはスパッタ法により成膜しているた め、膜厚が厚くなると成膜時間が長くなる。

- · ZrO<sub>2</sub>-SiO<sub>2</sub>ガラスは難エッチング材料であり、厚膜化によ りエッチングが困難になる。

- · Δの高いZrO<sub>2</sub>-SiO<sub>2</sub> PLCの導波路サイズを大きくした場 合, 高次モードが伝搬する導波路構造となる。

これらの問題点を回避するため、コアにGeO<sub>2</sub>-SiO<sub>2</sub>ガラスの 使用を検討する必要がある。テーパSSC以外にスポットサイ ズを拡大するための技術として逆テーパSSCが報告されてい る<sup>14)</sup>。逆テーパSSCではコアを小さくしていく事でスポット サイズも小さくなるが、Δに対してコアが一定のサイズよりも 小さくなると光がコアの外部に広がり、スポットサイズが拡大 する。5.5% の Δ を有する ZrO<sub>2</sub>-SiO<sub>2</sub> PLC にこの技術を適用して SMFと同程度までフィールド径を拡大する場合、コアサイズ は0.2 μm程度まで小さくする必要がある。しかしながら、 PLCのコアサイズを0.2 μm まで小さくし、そのサイズを正確 に制御する事は困難であり、SMFとの接続点でのコアサイズ 変動がスポットサイズ変動につながるため、安定して低接続損 失を得る事が困難となる。この問題を解決するためには二重コ ア型SSC<sup>15)</sup>が有効である。二重コアSSCでは第一コアが逆テー パになっており、第一コアを覆う形で第二コアを形成する事で、 第一コア末端部でのコアサイズの変動を吸収し、第二コア末端

部で安定したスポットサイズを得る事が出来る。ZrO<sub>2</sub>-SiO<sub>2</sub> PLCにこの構造を適用する場合、第一コアはZrO<sub>2</sub>-SiO<sub>2</sub>ガラス で構成し、第二コアはSMFに近いコア径とし、スポットサイ ズを近づけるためにGeO<sub>2</sub>SiO<sub>2</sub>ガラスを使用する必要がある。 しかしながら、この構成にした場合、第一コアと第二コアの膜 厚が大きく異なるため、第一コアと第二コアの結合部で大きな 損失が発生する。この問題を解決するためには第一コアと第二 コアの結合部でのコアサイズの差を小さくする必要がある。

#### 6.2 CVT-SSCの設計

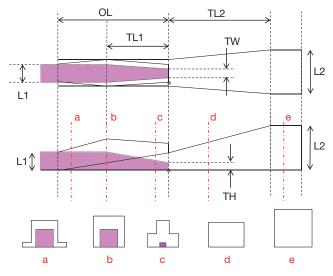

これらの問題点を解決し、ZrO2-SiO2 PLCとSMFのと接続 損失を低減するのに適したCVT-SSC(Cross Vertical Taper SSC) の構造を図16に示す。CVT-SSCは二重コア型SSCであ り、ZrO2-SiO2 PLCからなる第一コアは高さ方向、幅方向に逆 テーパとなっており、第一コア出射端でスポットサイズを拡大 している。第二コアはGeO<sub>2</sub>-SiO<sub>2</sub> PLCで構成され、高さ方向、 幅方向にテーパ形状となる。これにより、第一コアとの接続部 で接続損失を低減しつつ、出射部ではスポットサイズをSMF と同程度まで拡大し、SMFとの接続損失を低減している。

図16 CVT-SSCの構造 Structure of CVT-SSC.

CVT-SSCの設計パラメータを三次元ビーム伝搬法(3 dimension beam propagation method: 3D-BPM) を用いたシ ミュレーションにより最適化するため、まず最適な第二コアの  $\Delta$  ( $\Delta$ 2) と第二コアサイズ (L2) を計算した。この結果、 $\Delta$ 2を 1.5%, L2を11.5 μmとした。次に第一コアテーパ長 (TL1), 第 二コアテーパ長(TL2)の最適化を行った。この結果, TL1, TL2共に500 μm以上の長さとした場合に低接続損失が得れら る事が分かった。最後に第一コア末端部の幅(TW)と高さ(TH) を変化させて接続損失を計算した。この結果、目標とする接続 損失0.5 dB/facet以下を実現するためにはTWとTHをそれぞ れ0.8 μmと1.0 μm以下にすれば良い事が分かった。以上の結 果から、CVT-SSCの最適な設計パラメータを決定し、試作を 行った。

#### 6.3 CVT-SSCの試作結果

CVT-SSCの作製工程としては,

第一コア成膜→第一コア加工→第一コア Vertical Taper (VT1) 加工→第二成膜 (VT2) →第二コア加工→オーバーク ラッド成膜の順で行った。

VT1は、リソグラフィーでフォトレジスト (PR) に段差をつ け、このPRをエッチングマスクとしてドライエッチングをす ることで、垂直方向のテーパの形状を第一コアに転写させて形 成した。PR工程では、VT1を作製する部分に低い露光量で露 光することでPRを薄くする技術を応用した。露光時にショッ トの位置をずらしながら繰り返し露光する事で、多重露光する 回数を変化させ、現像後のPR厚に段差をつけた。

VT2は、第二コア成膜時にシャドウマスクを用いることに よって作製した。斜面の形状はシャドウマスクと基板間の距離 によって制御した。

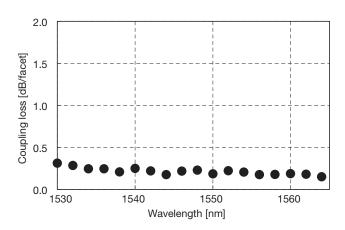

表2にCVT-SSCの設計値と試作結果を、図17にCVT-SSC を用いてZrO2-SiO2 PLCとSMFを接続した際の接続損失を示 す。この結果、CVT-SSCを用いる事で、波長1550 nm におけ る接続損失が0.2 dB/facetまで低減した。また、Cバンド全域 において0.31 dB/facet以下の接続損失を実現した。

CVT-SSCの設計値と試作結果 表2 Design and measured parameters of CVT-SSC.

| Parameter | Design  | Measured |

|-----------|---------|----------|

| TL1       | 500 μm  | 441 μm   |

| TL2       | 1000 μm | 1067 μm  |

| TW        | 0.5 µm  | 0.10 μm  |

| TH        | 0.1 μm  | 0.13 μm  |

図17 CVT-SSCを用いたZrO2-SiO2 PLCとSMFの接続損失 Coupling loss between ZrO2-SiO2 PLC and SMF using CVT-SSC.

### 7. おわりに

SiO<sub>2</sub>ガラスに添加するドーパントをGeO<sub>2</sub>からZrO<sub>2</sub>に変更 する事で、従来のPLCを大幅に上回る5.5%の△を有する超高 Δ PLCを実現した。製造工程を最適化する事で、ZrO<sub>2</sub>-SiO<sub>2</sub> PLCの伝搬損失は従来のPLCと同程度となる0.02 dB/cmに低 減した。ZrO2-SiO2 PLCを用いて超小型のコヒーレントミキサ を設計,試作し、4 mm×2 mmのチップサイズを実現した。 さらに、5.5%のΔを有するZrO<sub>2</sub>-SiO<sub>2</sub> PLCとSMFとの接続に おいて、構造を最適化したCVT-SSCにより、接続損失をCバ ンド全域で0.31 dB/facetに低減する事に成功した。

以上の結果から、小型化、低コスト化、高密度集積化が求め られる次世代の導波路型デバイスに対して、ZrO2-SiO2 PLCは 有望な技術である事を示した。

### 参考文献

- 1) 井上崇, 川島洋志, 松原礼高, 奈良一孝, 「石英系平面光導波 路を用いたPBS集積コヒーレントミキサの開発」、古河電工時 報, 第127号, pp. 11-16, 平成23年2月.

- 2) N. Matsubara, T. Inoue, and K. Nara, "Highly Polarization Maintaining Circuit-Based Dual PBS-Integrated Coherent Mixer with < 1degree Polarization Axis Rotation," in Proc. ECOC2012, paper We.3.E.5 (2012).

- 3) Y. Nasu, K. Watanabe, M. Itoh, H. Yamazaki, S. Kamei, R. Kasahara, I. Ogawa, A. Kaneko, and Y. Inoue, "Ultrasmall 100 GHz 40-Channel VMUX/DEMUX Based on Single-Chip 2.5%- $\Delta$  PLC," J. Lightwave Technol. vol. 27, no. 12, pp. 2087-2094, June 2009.

- 4) H. Yagi, N. Inoue, Y.Onishi, R.Masuyama, T.Katsuyama, T. Kikuchi, Y. Yoneda, and H. Shoji, "High-Efficient InP-Based Balanced Photodiodes Integrated with 90° Hybrid MMI for Compact 100 Gb/s Coherent Receiver," in Proc. OFC2013, paperOW3J.5 (2013).

- 5) U. Fisher, T. Zinke, J. R. Kropp, F. Amdt, and K. Petermann, "0.1 dB/cm waveguide losses in single-mode SOI rib waveguides," IEEE Photon. Technol. Lett., vol. 8, no. 5, pp. 647-648, May 1996.

- 6) Y. Nasu, K. Watanabe, M. Itoh, H. Yamazaki, S. Kamei, R. Kasahara, I.Ogawa, A. Kaneko, and Y. Inoue, "Ultrasmall 100 GHz 40-ChannelVMUX/DEMUX Based on Single-Chip 2.5%-Δ PLC," J. Lightwave Technol. vol. 27, no. 12, pp. 2087-2094, June 2009.

- 7) Jian-Jun He, Lamontagne B, Delage A, Erickson L, Davies M, and Koteles E.S, "Monolithic integrated wavelength demultiplexer based on a waveguide Rowland circle grating in InGaAsP/ lnP," J. Lightwave Technol. vol. 16, no. 4, pp. 631-638, Apr. 1998.

- 8) Samad M. Edlou, Ali Smajkiewicz, and Ghanim A. Al-Jumaily, "Optical properties and environmental stability of oxide coatings deposited by reactive sputtering," Appl. Opt., vol. 32, no. 28, pp. 5601-5605, Oct. 1993.

- 9) Fachun Lai, Ming Li, Kang Chen, Haiqian Wang, Yizhou Song, and Yousong Jiang, "Substrate temperature effect on the refractive index and a two-step film method to detect small inhomogeneities in optical films," Appl. Opt., vol. 44, no. 29, pp. 6181-6185, Oct. 2005.

- 10) "Zirconium and Hafnium" Mineral Commodity Summaries (US Geological Survey), pp.192-193. Jan. 2008.

- 11) David R. Lide, CRC Handbook of Chemistry and Physics 79th Edition, CRC Press, 1998.

- 12) Y. Hida, Y. Hibino, H. Okazaki and Y. Ohmori, " 10 m long silica-basedwaveguide with a loss of 1.7 dB/m," in Proc. IPR1995, paper IThC6-1 (1995).

- 13) M. Galarza, K. De Mesel, S. Verstuyft, C. Aramburu, I. Moerman, P. VanDaele, R. Baets, and M. Lopez-Amo, "1.55-µm InP-InGaAsPFabry-Perot lasers with integrated spot size converters using antiresonantreflecting optical waveguides," Photon, Technol. Lett., vol. 14, no. 8, pp.1043-1045, Aug. 2002.

- 14) T. Mizuno, M. Ito, T. Saida, T. Shibata, and Y. Hibino, "Optical spot sizeconverter using narrow laterally tapered waveguide for planar lightwavecircuits," J. Lightwave Technol. vol. 22, no. 3, pp. 833-839, Mar. 2004.

- 15) M. Tokushima, A. Kamei, and T. Horikawa, "Dual-Tapered 10um-Spot-Size Converter with Double Core for Coupling Polarization-Independent Silicon Rib Waveguides to Single-Mode Optical Fibers," Appl. Phys. Expr. 5, 022202, 2012.